Prying Eyes: A tale of two digital-video converters Pg 20

Technical and political suggestions for Detroit Pg 8

Throw those bits away Pg 18

Design Ideas Pg 48

Tales from the Cube Pg 62

### VOICE OF THE ENGINEER

# MAKING OSCILLATOR SELECTION CRYSTAL CLEAR

page 28

**VERIFYING FPGA** DESIGNS: SIMULATE, EMULATE, OR HOPE FOR THE BEST? Page 22

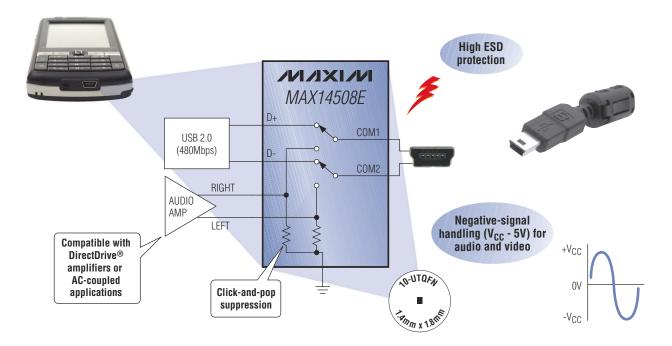

SUPPRESSING NONSTATIONARY NOISE IN MOBILE HANDSETS Page 38

PCIE CLOCK DISTRIBUTION IN EMBEDDED SYSTEMS Page 42

RENEW your FREE magazine

CLICK HERE TO

CLICK HERE TO **START** a FREE e-newsletter

# Put the burden of custom SoC and COT solutions on our shoulders.

#### Benefit from an integrated approach to SoC design

Choosing between a traditional ASIC or COT strategy can be tough. Fortunately, Toshiba makes your choice easier. We successfully implement ASIC, COT and RFCMOS product flows for customers who choose to move away from pure-play foundry models that entail high-risk IP and a high cost of ownership. With Toshiba, you get access to our more than 25 years of experience as an ASIC integrated device manufacturer, the engineering talent of the world's third largest<sup>1</sup> semiconductor company and reliable, proven manufacturing. We invest billions annually to stay at the forefront of process technology—from 90/65/40/32/22 nm. Join with Toshiba to achieve successful custom SoC and COT solutions.

#### Benefits

- Use Toshiba's proven IP at no cost, including PCI express, USB 2.0, DDR1/2/3, serial I/Os up to 8.5 Gbps

- Reduce costs with our reliable infrastructure, mask-making capabilities, die/package solutions and embedded memories

- Use your custom macros/differentiating IP to minimize competitive threats

- Validate design and silicon and package integrity before design start with Toshiba "Virtual Prototyping"

#### ChipQuest2 design challenge

Test your skill and win a Noise Cancellation Headset, Wireless Internet Hot Spot Finder, or high-powered flexible LED light (while supplies last). Enter at SoCworld.toshiba.com.

# YOUR SOURCE

HUNDREDS OF THOUSANDS OF PARTS HUNDREDS OF SUPPLIERS WWW.DIGIKEY.COM

1100.8

rovoedw W cron

## **17 YEARS IN A ROW!**\*

- **#1 Breadth of Product Line**

- **#1 Availability of Product**

- **#1 On-Time Delivery**

- #1 Responsiveness #1 Overall Performance

**Digi-Key Corporation purchases all product** directly from its original manufacturer.

\*Source: EE Times Distribution Study, August 2008 © 2008 Digi-Key Corporation

Quality Electronic Components, Superior Service

701 Brooks Ave. South • Thief River Falls, MN 56701 • USA

<sup>66</sup>At Averna, we used NI TestStand, NI LabVIEW, and PXI to create an RF testing solution including AM/FM, RDS, SIRIUS, XM, DAB, and IBOC, reducing total system costs by more than 50 percent.<sup>99</sup> – Richard Maltais, Vice President, Sales and Marketing, Averna

## NI TestStand, the Industry Standard in Test Management Software

Chosen by the top 10 global manufacturing companies, NI TestStand is a ready-to-run environment for developing, managing, and automating test sequences. NI TestStand works with any programming language and facilitates smoother integration with enterprise systems, getting you to first test faster.

#### NEW NI TestStand 4.1

- Ready-to-run environment increases efficiencies and test throughput

- Easy sequence flow, reporting, database logging, and connectivity to enterprise systems

- Built-in parallel and batch execution and synchronization

#### >> View demos and download free software at **ni.com/teststand**

#### 800 891 8841

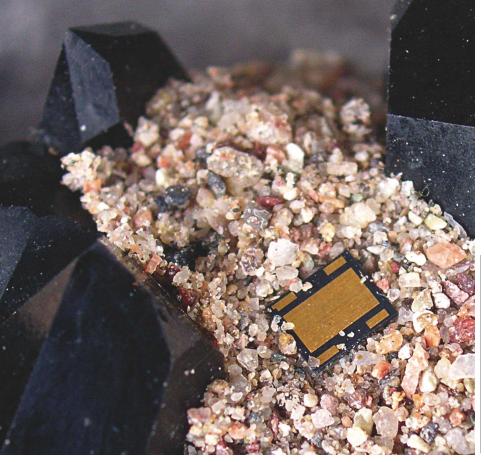

# Making oscillator selection crystal clear

28 Silicon and MEMS oscillators are joining venerable quartz crystals and ceramic resonators in the highly diverse oscillator market. You don't need a crystal ball to select the right device for your application, but some pertinent facts will help.

by Paul Rako, Technical Editor

Verifying FPGA designs: simulate, emulate, or hope for the best?

Simulation is a fact of life for many FPGA users today. But when is it time to stop simulating and just drop the design into the chip? by Ron Wilson, Executive Editor

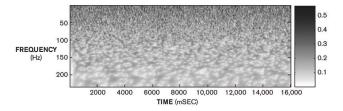

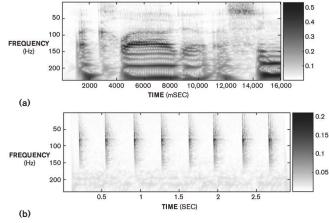

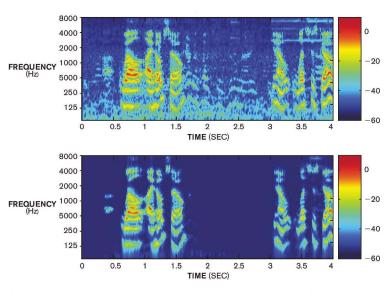

#### Suppressing nonstationary noise in mobile handsets

Book Mobile carriers are intimately aware of the role that voice quality plays in customer retention. One of the primary factors affecting voice quality is environmental noise, so any means of suppressing noise provides a potential differentiator for handset manufacturers. by Lloyd Watts, Audience

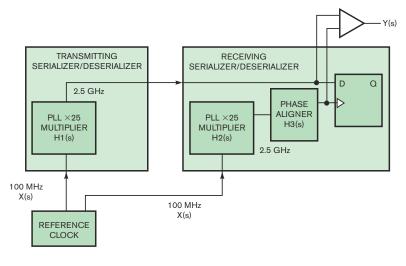

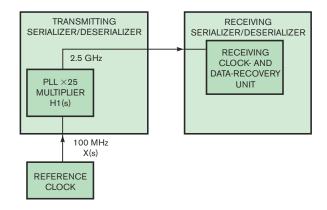

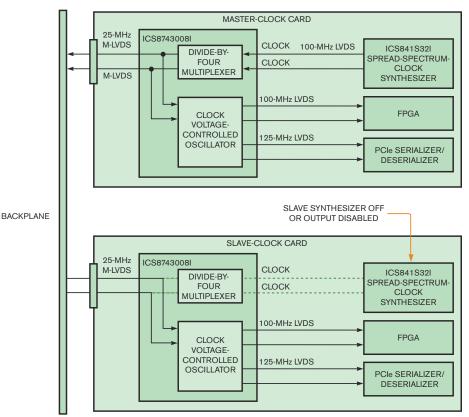

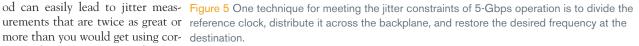

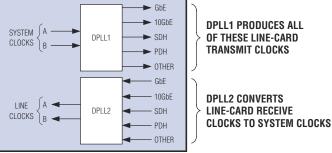

# PCIe clock distribution in embedded systems

4 2 As PCIe rapidly becomes the I/O interface of choice for high-performance systems, clock-distribution and jitter-reduction requirements create challenges for the embedded-systemdesign team.

by lan Dobson and Jim Holbrook, Integrated Device Technology Inc

# DESIGNIDEAS

|                                                        | PWM PULSE<br>TRAIN TEMPERATURE FEEDBACK                                                                                                                                                                                                                                               |   |  |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

|                                                        | 5V CONTROL POWER                                                                                                                                                                                                                                                                      |   |  |

| T                                                      | DIGITAL CLZD010                                                                                                                                                                                                                                                                       |   |  |

|                                                        | 1     FRK     ■     HEN 183       2     REF     □     STM     ■       3     ST7     = C     STM     15       5     GND     ■     0     = C S3133       7     FS0     ■     ■     = C S3133       9     PK3     +     ■     = C S3133       9     PKM     ■     = C S317     = C S3133 |   |  |

| PWM SETTING: COMPENSATION<br>31.2 kHz SETTING: 134 SEC |                                                                                                                                                                                                                                                                                       |   |  |

| -                                                      |                                                                                                                                                                                                                                                                                       | _ |  |

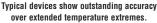

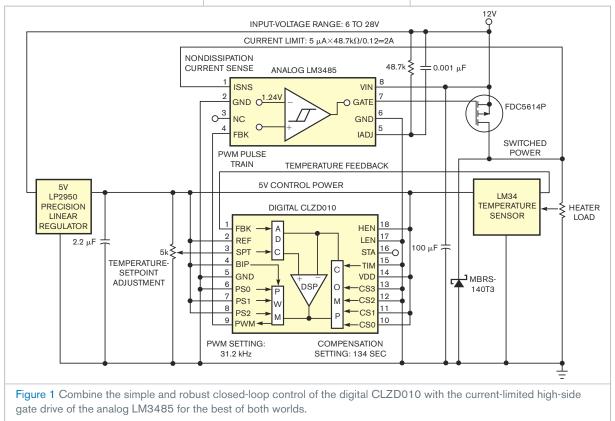

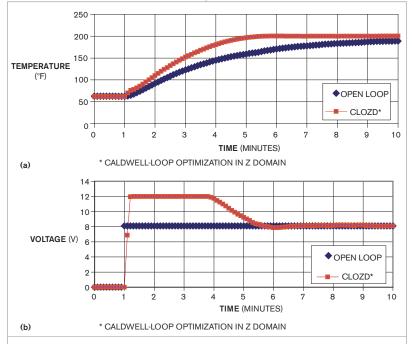

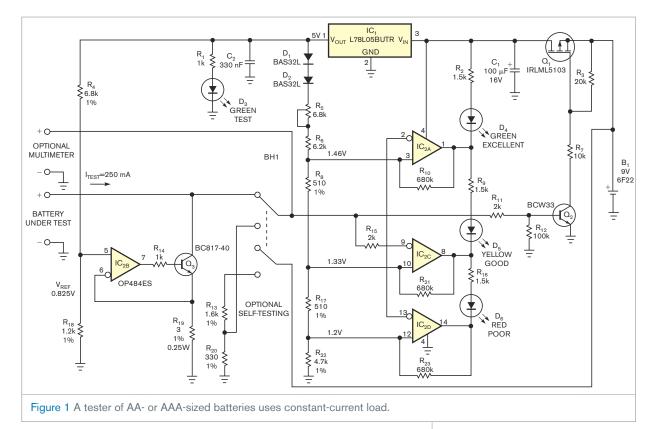

- 48 Digital controller compensates analog controller

- 51 Circuit provides constant-current load for testing batteries

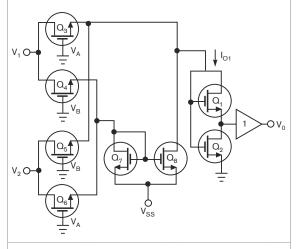

- 52 MOSFET-based, analog circuit calculates square root

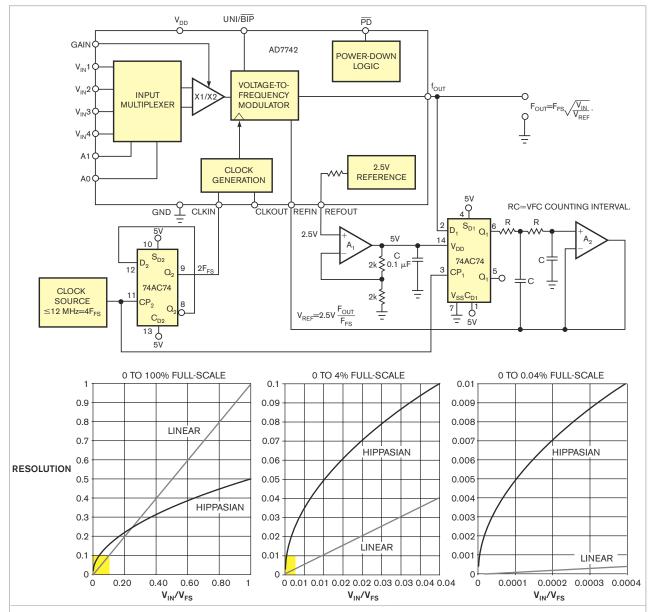

- 54 "Hippasian" nonlinear VFC stretches dynamic range

- 57 Decoder lights the way

# **Experience a Faster Way to Search for Components!**

Jameco Electronics' new catalog and enhanced Jameco.com website are two tools that are designed to work together to give electronic professionals faster access to the hottest components in the industry.

Color coded references throughout the catalog assist you in analyzing a wide range of brand choices (from franchise sourced to house brands to factory overruns) offering you more pricing options than you'll see anywhere else. Web codes allow you to quickly jump from catalog to website to view additional specifications, application notes, photos and more products. You'll find exactly what you're looking for without having to wade through hundreds of thousands of products on a complicated website or wielding a twenty pound catalog.

With a flip of the page or a click of the mouse, you have all the tools you need at your fingertips. Reach for Jameco first and order your catalog today.

Order your web-enabled catalog today!

Call 1-800-831-4242 or Visit www.Jameco.com/Speed for the ride of your life!

# contents 2.19.09

- 12 Companion processor supports video editing on the phone

- 13 Electric-car development spurs investment in US battery manufacturing

- 13 Instrument performs jitter-tolerance tests

- 14 PCIe Jammer provides inline-error injection

- 14 AMD and Virage Logic try a new model for third-party IP

- 16 **Voices:** Magma Design Automation's Rajeev Madhavan

# DEPARTMENTS & COLUMNS

- 8 **EDN.comment:** Technical and political suggestions for Detroit

- 18 Baker's Best: Throw those bits away

- 20 Prying Eyes: A tale of two digital-video converters

- 62 **Tales from the Cube:** Reversal of fortune

# PRODUCT ROUNDUP

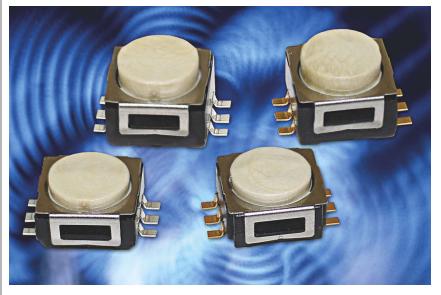

58 Switches and Relays: Snap-action key switches; triac photocouplers; load, rocker, and powerdistribution switches; and push-in terminals

EDN @ (ISSN#0012-7515), (GST#123397457) is published biweekly, 24 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer, Mark Finkelstein, President, Boston Division. Periodicals postage paid at Littleton, CO 80129 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80129-2345. Barch, CO 80163-7500. EDN® copyright 2009 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issue: US, \$179.99 one year, Canada, \$2299 one year. (Includes 7% GST, GST#123397457); Mexico, \$229.99 one year, air expedited, \$399.99 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication: Volume 64, Number 4 (Printed in USA).

# The Newest Microcontrollers

**HEEEEE**

#### <u>New Products from:</u>

MICROCHIP PIC32 Microcontrollers www.mouser.com/ microchip/a

### Founded by Philips

LPC2478/2470 ARM7™ Microcontrollers www.mouser.com/nxp/a

TEXAS INSTRUMENTS Authorized Distributor MSP430 Ultra-Low Power Microcontrollers www.mouser.com/ ti-msp430

#### The ONLY New Catalog Every 90 Days

Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 366 leading suppliers.

a tti company

The Newest Products For Your Newest Designs

(800) 346-6873

www.mouser.com

Over A Million Products Online

# EDN) at edn.com

EXPANDED ENGINEERING COVERAGE PLUS DAILY NEWS, BLOGS, VIDEO, AND MORE.

#### ONLINE ONLY

Check out these Web-exclusive articles:

## EoPDH as an alternative for delivering rich-media applications

This study compares the performance of media-delivery techniques to show how EoPDH (Ethernet-over-plesiochronousdigital-hierarchy) technology can deliver reliable, resilient transport services for streaming-video applications. →www.edn.com/article/CA6624633

### Jasper, OneSpin seek broader audience for formal-verification tools

Not just for verification experts anymore: New tools try to attract designers at early stages of the design process.

→www.edn.com/article/CA6631000

### Forging new ground using existing COMs concepts

Although they are highly popular embedded-computing components, COMs (computers on modules) lacked the continuity needed to make these boards appeal to the various industries for which they were designed.

→www.edn.com/article/CA6631704

# INNO ATION VOTE NOW!

Tune in to www.edn.com/innovation to see the innovative engineers and products our editors selected as finalists in this year's *EDN* Innovation Awards. After perusing the candidates, help us honor electronic innovation by using the easy electronic ballot to make your voice heard.

READERS' CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

### Evaluating value-oriented x86 CPUs: the price of falling prices

Economical microprocessors may enable you to easily hit your next design's billof-materials cost target, but will they also allow you to accomplish your performance and power-consumption objectives? →www.edn.com/article/CA6625435

Outsourcing in a troubled economy →www.edn.com/article/CA6628835

A bad-capacitor story ends happily →www.edn.com/article/CA6625453

#### MIT researchers claim 50% increase in solar-cell output

→www.edn.com/article/CA6625447

#### Supply chains and the "weakest-link" problem

→www.edn.com/20090219toca

### Intel invests \$23 million in three Indian companies

→www.edn.com/article/CA6629515

#### **FEED YOUR NEED** Belly up to the *EDN* Product fEEd, our ongoing buffet of new components, ICs, tools, and more.

→www.edn.com/productfeed

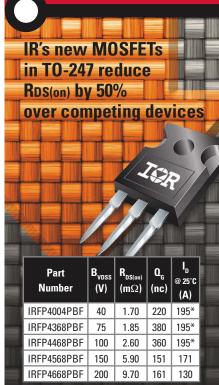

# Benchmark MOSFETs

\* Package limited

#### Features

- Suited for Synchronous rectification, active ORing, industrial battery and DC to AC inverters

- Industrial grade and MSL1

- Lead free, RoHS compliant

For more information call 1.800.981.8699 or visit http://www.irf.com

EDN.COMMENT

#### BY RICK NELSON, EDITOR-IN-CHIEF

# Technical and political suggestions for Detroit

o the Detroit automakers deserve a bailout, or should they be left to go the way of the dinosaurs (**Reference** 1)? Perhaps there are other options. In a recent article, Sebastian Thrun, a professor of computer science at Stanford University, and Anthony Levandowski, now a product manager at Google, discuss "four technologies

that could be put on the road in the next several years." They describe these technologies, some of which they say they invest in, as win-win

situations, which alone or in combination can increase energy efficiency, improve safety, cut pollution, and make commuting more convenient (**Reference 2**).

Those technologies, they write, include Wi-Fi-like dedicated shortrange communication, which enables cars to form ad hoc networks with one another and with roadway infrastructure; automatically controlled X-bywire capabilities that would allow robotic cars to drive in tight formation under computer control (Reference 3); solar/electric-hybrid technology, in which solar panels on one garage provide power for 10,000 miles of driving per year; and smartphone-like onlinecommunications capabilities that will help drivers find parking spaces, make restaurant reservations, and purchase songs they hear on the car radio.

On the eve of Obama's inauguration, auto-industry journalist Steve Parker detailed his own ideas for saving Detroit (**Reference 4**). Parker's recommendations are a political wish list of what he would like the incoming administration to do. He suggests that we begin an Apollo-like program to deploy "the first national infrastructure for hydrogen- and natural-gas fuels" and build fuel-cell-based vehicles that can run on these fuels. He also suggests raising federal gasoline taxes and instituting tax rebates and other incentives for purchasers of highmileage, clean vehicles. He'd like Detroit to become involved in the development of modern high-speed-rail and light-rail systems. And he'd like government to mandate that automakers achieve CAFE (corporate-averagefuel-economy) levels of 35 mpg—currently slated for 2020—by 2015.

Both groups of suggestions have some good ideas but no silver bullets. As for the technical solutions, technologies for robotic cars to drive in tight formation or for the deployment and use of a hydrogen infrastructure seem impractical in the short term; I wouldn't advocate extensive public financing for R&D in either area. CAFE standards have had the perverse effect of encouraging the Big Three to heavily market profitable SUVs and trucks to offset losses incurred in selling fuelefficient autos. Tax rebates on fuelefficient cars coupled with higher gas taxes or sales surtaxes on low-mileage cars might be a better approach, although a surtax on low-mileage vehicles would unfairly penalize individuals and families that need trucks or large cars for occasional use. (Commercial vehicles could be exempt from this surtax.) As for involving Detroit in rail projects, well, OK, but why would the Big Three be more successful in making trains than in making cars?

Solar/electric-hybrid technology shows promise. If the technology is not ready for home installation, perhaps employers and commercial establishments could offer solar-enabled parking as a perk for employees and customers. Ad hoc networking schemes and enhanced online-communications capabilities also hold promise-especially if public investment in roads and bridges could help put the electronic infrastructure in place to provide realtime information on traffic and roadway conditions and on nearby services and points of interest.EDN

#### REFERENCES

Nelson, Rick, "Evolution and Innovation, *EDN*, Jan 22, 2009, pg 8, www. edn.com/article/CA6629470.

Thrun, Sebastian, and Anthony Levandowski, "Four Ways for Detroit to Save Itself," *The New York Times*, Jan 3, 2009, www.edn.com/ 090219eda.

Nelson, Rick, "Balancing act," Test & Measurement World, March 2005, pg 30, www.tmworld.com/article/ CA506541.

Parker, Steve, "Five Things Mr. Obama Must Say About Detroit-and Fast," *The Huffington Post*, Jan 19, 2009, www.edn.com/090219edb.

Contact me at rnelson@reedbusiness. com.

+ Go to www.edn.com/090219ed and click on Feedback Loop to post a comment on this column.

+ www.edn.com/edncomment

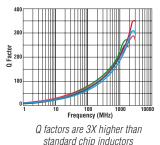

# 29 More Q. Less Cu

# These tiny new air core inductors have the highest Q and current handling in the smallest footprint.

Coilcraft's new SQ air core inductors have unmatched Q factors: most are above 200 in the 1-2 GHz range! That's 3 times higher than comparably sized 0805 chip coils.

←1.83 mm→

DER DIRECT

100-322-2645 ORDER BY 5

COW

RoH

DELIVERY

And with their extremely low DCR, they can handle 4 to 8 times more current: up to 4.4 Arms.

SQ air core inductors are perfect for your LC filter and RF impedance matching applications. They come in 15 values ranging from 6 to 27.3 nH, all with 5% tolerance.

These coils

are significantly smaller than existing air core inductors. We reduced the footprint by using close-wound construction and keeping the leads close to the body. The square shape cuts the height to as low as 1.5 mm and creates flat top and bottom sur-

faces for easy automated handling and stable mounting.

The square shape and narrow footprint reduce board space by 60-75% over conventional air core inductors.

See how the ultra-high Q and

current handling of Coilcraft's new SQ air core inductors can maximize the performance of

your next design. For complete specifications and free evaluation samples, visit www.coilcraft.com/sq

Coilcraft

#### More measurements. More data. Less cost.

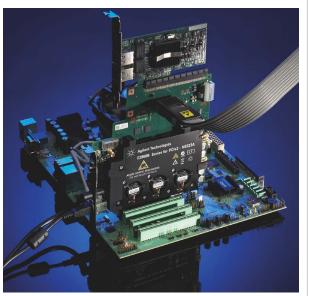

With up to 560 channels of data logging at a maximum scan rate of 1000 channels/sec, an internal 6 ½ digit DMM with 22-bit resolution, and 0.03% accuracy, it's no mystery why Agilent's data acquisition systems are among the top selling in the world. The 34970A and 34980A are both at home with either data acquisition or functional test, with a broad selection of plug-in modules.

Now with Agilent Data Logger Pro software, you'll be able to collect data, check limits, perform extensive branching, and view and store the data without authoring the programming yourself. It's an ideal expansion at a significant savings.

#### www.agilent.com/find/daqswitch

u.s. 1-800-829-4444 canada 1-877-894-4414

# **Agilent Technologies**

PRESIDENT, BOSTON DIVISION, REED BUSINESS INFORMATION Mark Finkelstein, mark.finkelstein@reedbusiness.com: 1-781-734-8431

PUBLISHER, EDN WORLDWIDE Russell E Pratt, 1-781-734-8417; rpratt@reedbusiness.com

ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes, 1-408-421-3799; judy.hayes@reedbusiness.com VICE PRESIDENT, EDITORIAL DIRECTOR

Karen Field, 1-781-734-8188; kfield@reedbusiness.com EDITOR-IN-CHIEF, EDN WORLDWIDE

Rick Nelson, 1-781-734-8418; rnelson@reedbusiness.com

Ron Wilson, 1-408-345-4427; ronald.wilson@reedbusiness.com MANAGING EDITOR

Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com Contact for contributed technical articles

EDITOR-IN-CHIEF, EDN.COM Matthew Miller 1-781-734-8446; fax: 1-303-265-3017;

mdmiller@reedbusiness.com SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

ANALOG Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com EMBEDDED SYSTEMS

Warren Webb, Technical Editor 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187;

bdipert@edn.com MICROPROCESSORS, DSPs, AND TOOLS Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116;

rcravolta@edn.com NEWS Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

DESIGN IDEAS EDITOR Martin Rowe

edndesignideas@reedbusiness.com SENIOR ASSOCIATE EDITOR Frances T Granville, 1-781-734-8439;

fax: 1-303-265-3131; f.granville@reedbusiness.com ASSOCIATE EDITOR

Maura Hadro Butler, 1-617-276-6523; mbutler@reedbusiness.com EDITORIAL/WEB PRODUCTION

Diane Malone, Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442; fax: 1-303-265-3198 Melissa Annand, Newsletter/Editorial Coordinator 1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-303-265-3042 CONTRIBUTING TECHNICAL EDITORS Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com COLUMNISTS

> Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn; Pallab Chatterjee PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Jones, Production Manager 1-781-734-8328; fax: 1-303-265-3164

EDN EUROPE Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; agrophet@reedbusiness.com

#### EDN ASIA

Susie Newham, Managing Director susie.newham@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn *EDN JAPAN* Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

DENNIS BROPHY Director of Business Development, Mentor Graphics DANIS CARTER

Principal Engineer, Tyco Healthcare CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne DMITRII LOUKIANOV System Architect. Intel

> RON MANCINI Retired Staff Scientist GABRIEL PATULEA

Design Engineer, Cisco DAVE ROBERTSON

Product Line Director, Analog Devices SCOTT SMYERS

VP Network and System Architecture Division, Sony TOM SZOLYGA

Program Manager, Hewlett-Packard JIM WILLIAMS

Staff Scientist, Linear Technology EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000.

Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag. com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, C0 80129-2345. Include your mailing label.

# **MAXIMUM** PRECISION

#### From a full spectrum of pin receptacles

Regardless of whether your components fly with the Blue Angels or control industrial robots, good design should never be limited by a lack of options. Mill-Max Mfg. Corp. offers hundreds of high-precision receptacle styles with an unprecedented range of options and features:

- 35 pre-tooled contact styles.

- A full selection of 3-, 4- and 6-finger contact designs.

- .008" to .102" (0,20 2,59mm) pin acceptance.

- Accepts round, square and rectangular component leads.

- Styles for soldering, swaging or press-fitting.

Large Variety of Styles

**Knock-out Bottom OFP®**

Available on Tape and Reel

# Mill-Max receptacles. Plug into the simple, reliable connectivity solution.

To view our Design Guide, new product offerings and order free samples, visit

www.mill-max.com/EDN585

#### EDITED BY FRAN GRANVILLE

#### INNOVATIONS & INNOVATORS

## Controller targets mobile robots

Robot technology is appealing to embedded-system designers not only because of the mechanical-control aspect but also because of the potential it has to shield humans from dangerous and even life-threatening situations. Targeting the high end of this technology, Roboteq recently introduced an intelligent, dual-channel dc-motor controller that can directly drive as much as 120A on each channel at voltages as high as 60V. The AX2860 should appeal to designers of mobile-

The intelligent, dual-channel AX2860 dcmotor controller can directly drive as much as 120A on each channel at voltages as high as 60V.

robotic vehicles, including AGVs (automatic guided vehicles), underwater ROVs (remotely operated vehicles), and mobile robots for exploration, hazardous-material handling, and military and surveillance applications.

The controller accepts commands from standard radios for simple remote-controlledrobot applications, analog joysticks, or RS-232 interfaces. Using the serial port, you can use the AX2860 to design autonomous or semiautonomous robots by connecting it to singleboard computers, wireless modems, or Wi-Fi adapters. You can operate the controller's two channels independently or combine them to set the direction and rotation of a vehicle by coordinating the motors on each side for tanklike steering. You can operate the motors in open- or closed-loop speed mode. The AX2860 includes inputs for two quadrature encoders operating as fast as 250 kHz and four limit switches for precise speed and traveled-distance measurement. The AX2860 is available now at \$720 in single quantities and comes with cable and PC-based configuration software.-by Warren Webb

**Roboteq**, www.roboteq.com.

- FEEDBACK LOOP "If all the dinosaurs had gone extinct, we would not have birds. A lesson for world corporations: Most of the largest species in history have outgrown their environment. Smaller species are much more adaptable and quicker to adopt chanaes."

—Engineer and EDN reader Charles Warner, in EDN's Feedback Loop, at www.edn. com/article/CA6629470. Add your comments.

#### Companion processor supports video editing on the phone

Semiconductor start-up Movidia has announced the MA1110 multimedia processor for mobile phones. The MA1110 operates as an attached processor to the baseband or to another applications processor in medium- to high-end phone designs to enable high-performance inphone-video postproduction in real time on low power budgets.

The concept supports social-networking applications on phones in which users capture, edit, and publish video without using a PC. The chip includes interfaces to dual cameras with resolution as high as 12M pixels, the host processors, displays, and external memory when necessary; 1.4 Mbytes of memory is on-chip. The chip has a host RISC processor and extensive graphics-manipulation IP (intellectual property) hard-coded into silicon. It performs complex video-editing tasks, such as real-time image stabilization, super-resolution zoom, slow motion, and color matching.

The MA1110 also supports the high

resolutions of all standard audio and video codecs and APIs (application-programming interfaces) to ensure full compatibility with a range of content, and it can perform transcoding between the standards.

Movidia has first silicon now and expects to offer production-quality silicon for sampling by midyear. The chip consumes approximately 200 mW when performing intensive graphics operations, the company predicts.—**by Graham Prophet Movidia**, www.movidia.com.

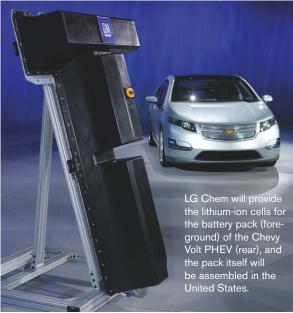

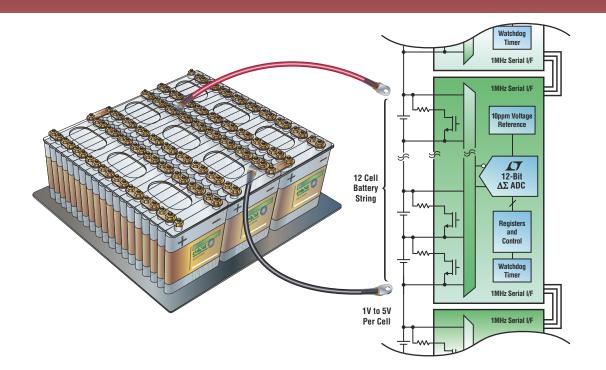

## Electric-car development spurs investment in US battery manufacturing

t last month's Detroit Auto Show, General Motors announced that LG Chem, a Korean lithiumion-battery-cell manufacturer, will be providing the cells for the Chevy Volt PHEV (plugin-hybrid-electric vehicle). GM made much of the fact that it will keep assembly of the battery *pack* in the United States. However, the guts of a battery pack-in weight, cost, and intellectual property-are in the cells, of which the United States has apparently fallen off the map in being a volume producer.

Contrast these start-up ventures with BYD's F3DM PHEV, which it unveiled a few weeks ago in China and planned to begin selling in the United States in 2011, priced at around \$20,000. BYD got its start making after-market lithium-ion batteries for cell phones, and got into the EVbattery market on the strength of its founder's belief that the future of transportation lies in EVs. The company has more than 20 years' experience developing and manufacturing lithium-ion batteries.

Innovation over the long haul

in a technology often goes hand in hand with volume production. The United States may be unable to retake and maintain a lead in battery development unless it also keeps the manufacturing here.

But maybe there's hope: In a briefing to a US Senate committee, Kleiner Perkins' venture capitalist John Doerr claimed that a US company "somewhere in the Midwest" is manufacturing a stable, durable lithium-ion battery with higher effective-storage capacity. "The result is [that] electric vehicles will be able to travel twice as far and, eventually, three times as far, to over 100 miles before recharging," he says. Kleiner Perkins is investing in the company, but would give no details, such as the company's name or what the actual battery specs are.

In addition, researchers at the University of Michigan have spun out Sakti3, a Michiganbased battery start-up. The venture-capital community has invested \$2 million in Sakti3, and the state of Michigan has put in \$3 million, with \$2.4 million in tax credits. Again, no word on when we can expect to see the batteries.

-by Margery Conner **Chevy Volt**, www.chevrolet. com/electriccar. **BYD Auto**, www.byd.com.

BACK.

000

#### INSTRUMENT PERFORMS JITTER-**TOLERANCE TESTS**

02.19.09

Agilent Technologies' new N4903B J-BERT (bit-errorratio tester) enables you to accurately characterize and test compliance of next-generation devices that support multigigabitper-second serial-bus standards, such as PCIe (peripheral-component-interconnect-express) 2.0, USB (universal serial bus) 3, QPI (QuickPath interconnect), Hypertransport 3, and FB-DIMM (fully buffered dual-inline-memory module) 2. According to Agilent, the instrument's high characterization accuracy enhances the robustness of the design under test.

QPI, Hypertransport, and FB-DIMM 2 operate with forwarded clocks that run at half the data rate, confronting design teams with additional test challenges when characterizing receivers under real-world stress conditions.

Prices start at \$139,000 for the 7-Gbps version, and \$179,000 for the 12.5-Gbps version. For an expanded description of this product, go to www.edn.com/ article/CA6633282.

-by Dan Strassberg Agilent Technologies, www.agilent.com/find/ jbert.

The B version of J-BERT tests and verifies the operation of both forwarded- and embedded-clocked ICs under a variety of signal impairments at data

#### **DILBERT By Scott Adams**

# pulse

## PCIe Jammer provides inline-error injection

gilent Technologies has introduced the N5323A Jammer inline-error-injection tool for PCIe (peripheral-component-interconnectexpress) protocol testing. This unit allows you to shorten test cycles and improve time to market for peripheral and host devices. PCIe has become the interconnect technology of choice in high-performance applications, including servers, storage devices, peripherals, and graphics adapters. Designers of PCIe systems and devices face demands for more reliable systems that can interoperate with the rapidly increasing number of PCIe devices.

Agilent designed the N5323A to address these challenges. The half-size PCle plug-in unit measures 6.6 in. long and 7.1 in. high. It sits transparently between the host and a peripheral adapter and can modify PCle data transfers in real time to cre-

The PCIe Jammer injects errors to perform disruptive tests on live PCIe systems regardless of the operating system or application software.

ate disruptive scenarios that increase test coverage. The unit performs these disruptive tests in live systems regardless of the operating system or application software. You can program almost any error-recovery test case, including correctable and uncorrectable PCIe errors. With this approach, you can improve error handling and avoid costly last-minute product changes or recalls. Because of its transparency, setting up the unit is fast and easy. You need write no scripts; a graphical sequencer drives the error injections.

To seamlessly move from testing to debugging, the Jammer also works with the manufacturer's PCIe E2960B protocol analyzer. The Jammer generates errors and can trigger the analyzer to capture and display the responses. This arrangement allows you to view traffic both before and after the error injection to ensure that your application invoked the appropriate recovery mechanism. Versions of the Jammer support PCIe implementations that have one, four or fewer, and eight or fewer lanes, as well as data rates of 2.5G and 5G transfers/sec. Prices start at \$27,500.

-by Dan Strassberg > Agilent Technologies, www.agilent.com/find/pcie jammer.

### PRACTICAL CHIP DESIGN AMD and Virage Logic try a new model for third-party IP

EDNBLOG

An innocuous-looking announcement on the wires last month from AMD (www.amd. com) and Virage Logic (www. viragelogic.com) didn't sound like much. But it may be the sound of the curtain coming up on a whole new business model for the third-party IP (intellectual property) business—and none too soon.

Virage and AMD announced that the two companies would collaborate on the development of silicon IP, including some specific interface cores now and unspecified new cores in the future. The cores currently being productized are a Generation 2 PCIe (peripheral-component-interconnect-express) interface, an HDMI (highdefinition-multimediainterface)/DisplayPort interface, and a MIPI

(mobile-industry-processorindustry) core. All three are to be available in both 65- and 40-nm versions.

So far, it doesn't sound like a big deal. But ... it might be the beginning of a big deal. The graphics division of AMD, the former ATI, developed the three interface cores for internal use in standard bulk CMOS, not for the processor division's more esoteric SOI (silicon-on-insulator) process. And AMD has proved all three not only in silicon but in systems at 40 nm. Virage intends to pick up the cores as is, prepare them for commercialization as for-sale, third-party IP,

and then market them.

Virage, one of the leaders in logic-cell libraries, embedded-RAM compilers, and, more recently, interface IP, has supplied the AMD designers for years. Neither the former ATI nor any other part of AMD has a history in the IP business. So, why does the IP vendor now want to license IP from its customer?

The cynic might suggest part of the answer is that AMD needs all the revenue sources it can find right now and that it would commercialize its employee lunchroom if it could figure out a business model. But Brani Buric, Virage's executive vice president of marketing and sales, says that ... part of the equation is time to market. AMD engages with its foundries on a new process node at about the same time that Virage begins developing logic libraries—very early. So

... AMD will have complex interface cores ... up and working much earlier than would normally be feasible.

#### -by Ron Wilson

►www.edn.com/practicalchip design.

► For the full post, go to www. edn.com/090219pa.

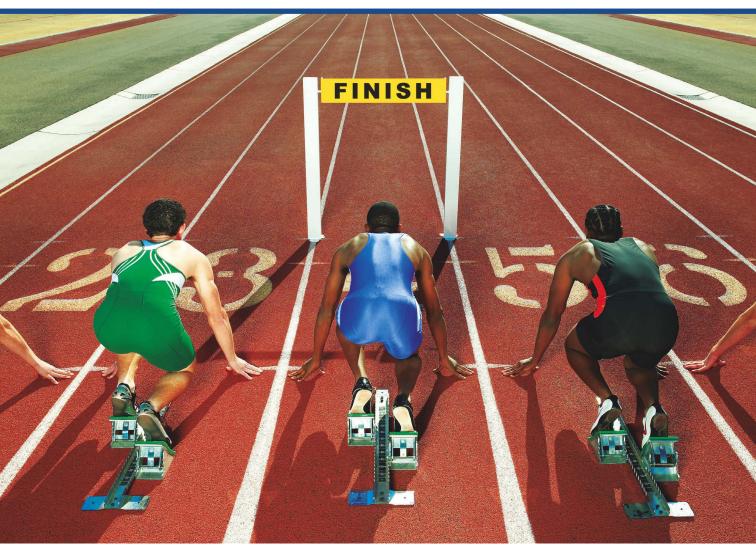

# TAPE-OUT COMES A LOT FASTER WITH CALIBRE NMDRC.

INTEGRATED SYSTEM DESIGN + DESIGN FOR MANUFACTURING + ELECTRONIC SYSTEM LEVEL DESIGN + FUNCTIONAL VERIFICATION

**Calibre® nmDRC** There's nothing like having an advantage when you're racing to market. That's exactly what you get with Calibre nmDRC. Widely recognized as the world's most popular physical verification solution, Calibre's hyperscaling architecture produces the fastest run times available. To accelerate things even more, Calibre nmDRC adds incremental verification and a dynamic results-viewing and debugging environment. Designers can check, fix and re-verify DRC violations in parallel, dramatically reducing total cycle time. Start out and stay ahead of the pack. Go to mentor.com/go/calibre\_nmdrc or call us at 800.547.3000.

## VOICES Magma Design Automation's Rajeev Madhavan

The evolving EDA business, the depressed economy, the state of the semiconductor industry, and the future of education in the United States were all on the mind of Rajeev Madhavan, chairman and chief executive officer of Magma Design Automation, when he spoke recently with *EDN*. The following is an excerpt from that interview. For the full discussion, got to www. edn.com/090219pb.

#### What's your impression of the state of the semiconductor industry?

A October and November were the worst months I have ever seen in my life. People deploying new technology just stopped halfway through their projects.

### What's going to happen next?

Companies are doing some analysis to determine what they are to become. Right now, semiconductor companies are shedding what they think is bad for them, and many are moving away from large digital SOCs [systems on chips] and toward mixed signal.

#### Why is that?

It's just a reflection of the fact that just putting a digital SOC together by slapping a lot of IP [intellectual property] into design and coming up with a chip that is sufficiently differentiated from the competition is very difficult.

Could you comment on Magma's recent evolution?

Magma came out with a physical-synthesis tool in 2005, and we went through a period where we had a lot of litigation expenses. But we came out of that where we actually had a new tool, Talus. By June 2008, we finished the transition in technology, and, as of November, pretty much every customer had migrated over to the Talus platform. But what has helped us through the transition period is our analog technology, which has kicked into very high gear.

# What are the challenges in the mixed-signal-EDA market?

If you look at the history of mixed-signal and analog tools, there has really been only one player, which is Cadence. I participated in the development of the Cadence tools in 1991, and very little has changed. The flow is very manual. There was never an automated way of transferring the knowledge of a great circuit-design engineer to the layout.

What has Magma done to

## address the analog-design challenges?

Rather than competing head-on with Cadence, we provide automated capabilities in our Titan tool. It's extremely fast and allows high-caliber circuit designers to capture a design, verify the design, and then in an automated fashion transfer it to a given process.

In fall 2007, you sat down with an *Electronic Business* editor and some other executives to discuss education [see www.edn.com/article/CA6487765]. In that interview, you said that, in the United States, too few engineers are graduating and that math and science have to be elevated in the middle- and high-school levels. Have you seen any improvement over the past year?

Some of the problems of finding enough engineering graduates to hire have been dampened by the recession, but the reality is that, as far as education in the United States goes, we've got a lot of work to do.

#### What are the prospects for making those improvements?

A I am very hopeful about what the new administration is going to do. At least [the administration is] cognizant of the problem that exists—that there is very little emphasis on getting kids to go into technology areas. It's time we changed that and got back into leadership in every area of education—from kindergarten to college-engineering programs.

## What's the solution-spend more money?

Money is one aspect. A In addition, the metrics of how we measure student performance are somewhat arbitrary. And our teachers don't foster competitiveness. We want to accommodate the sensitivities of our students, but, when our students graduate, they'll be in a competitive world. I'm not an educator, but I think we can introduce that competition much earlier in the system without having a negative impact on the kids.

-Interview conducted and edited by Rick Nelson

# **Optimum process control means efficiency, reliability, and Analog ICs.**

#### Ultralow Noise, 24-Bit $\Sigma$ - $\Delta$ ADC with PGA: AD7190

Expand the operating speed and precision of sensitive measurement instruments with the industry's best combination of data rate and noise-free resolution.

#### 16-Bit User-Programmable Current and Voltage Output DACs: AD5422 Family

Single platform simplifies system design by offering improved performance and a high level of control functionality in a compact package.

36 V, Micropower, Dual, Single-Supply Amplifier: ADA4091-2

Eases front-end design by offering integrated input protection, high accuracy, reduced power, and very small package. Developed through advancements in Analog Devices' proprietary  $iPolar^{TM}$ process technology.

#### Precision Instrumentation Amplifier: AD8221

Affordable and easy to use. Industry-leading performance in a small package for high channel density applications.

#### Current/Voltage Output Drivers: AD5750 and AD5751

Increase efficiency by offering best-in-class performance with the industry's highest level of accuracy and diagnostic capability.

#### Low Power, High Precision Analog Microcontrollers: ADuC7060 Family

Combine 24-bit  $\Sigma$ - $\Delta$  ADCs with 16- and 32-bit ARM7TDMI<sup>®</sup> MCUs and Flash/EE memory for unequaled multichannel data acquisition and processing performance.

# P

analog is everywhere."

# Dependable systems, advanced manufacturing, secure environments: Analog Devices

Instrumentation and process control equipment manufacturers are helping their customers to achieve increased line efficiency, productivity, and safety by leveraging advancements in analog technology. For more than 40 years, designers of industrial equipment have relied on Analog Devices' innovations to distinguish their products and to control and protect their customers' valuable equipment assets. And in today's cost- and safety-sensitive industrial world the speed, precision, and integration of ADI process control ICs enable whole new levels of capabilities—and possibilities.

Experience what Analog Devices can do for your designs. Learn more about our newest application-tuned ICs and support tools by visiting *www.analog.com/industrial-ad*.

BAKER'S BEST

#### **BY BONNIE BAKER**

## Throw those bits away

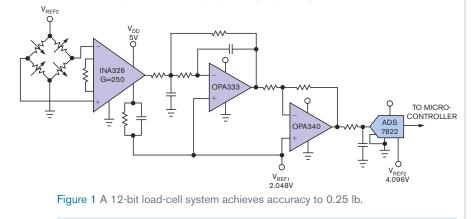

high-quality load cell may have a 2-mV/V output-transfer function, meaning that for each volt of excitation you get  $\pm 2$  mV of the full-scale output signal. With an excitation of 4.096V and a full sensor deflection, the maximum output is  $\pm 8.192$  mV. In a 12-bit application, half of full-scale might represent 0 to 250 lbs for a bathroom scale. If you want 0.25-lb resolution, you need 1000 points of measurement output. To look at something that is 1/1000th of the full-scale range, you

must distinguish a change of  $8.192 \mu V$ of the sensor output. You can achieve this distinction by keeping the peakto-peak sensor noise less than  $8.192 \mu V$  for 99.999% of the time, using a crest factor of 4.4 (**Reference 1**). With this definition, the least-significant bit at the sensor is  $8.192 \mu V$ , or 931 nV rms.

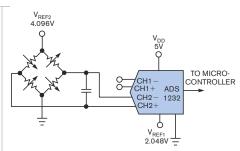

The load-cell bridge has an excitation voltage of 4.096V (Figure 1). The INA326 instrumentation amplifier follows the load cell with a gain of 250V/V. The system's full-scale voltage,  $250 \times \pm 8.192$  mV, produces a  $\pm 2.048V$  full-scale signal. The 12-bit ADS7822 digitizes the analog signal. This 12-bit converter system must have an analog filter. The lowpass OPA333 (www.ti.com/opa333) analog filter's primary function is to remove the high-frequency signal components at the input of the ADC (**Reference 2**). Because the load cell in the circuit operates near dc, you limit the bandwidth to 10 Hz. The components in **Figure 1** cost less than \$6.

Now, look at load-cell measurement with a 24-bit system. You can simply put the load-cell signal through a firstorder lowpass filter and into the delta-sigma ADC (**Figure 2**). The firstorder filter in this circuit eliminates high-frequency noise around the con-

Figure 2 A 24-bit load-cell system has greater-than-0.25-lb accuracy.

verter's sampling frequency (**Reference 3**). The sensor provides the resistor for the filter RC pair.

Look at the errors for the 24-bit delta-sigma system in **Figure 2**. The ADS1232 (www.ti.com/ads1232) produces 3.7  $\mu$ V p-p of noise, with a crest factor of 4.4. This figure is much lower than the sensor's least-significant bit. Additionally, the full-scale range of the converter is 4.096V, whereas the sensor's full-scale output range is  $\pm$ 8.192 mV. As you can guess, you will "throw away" most of the output bits of the delta-sigma converter. The components in **Figure 2** cost less than \$4.

You may find that the 12-bit converter system ends up costing you more money, real estate, and headaches than the alternative 24-bit system.**EDN**

#### REFERENCES

Baker, Bonnie, "RMS and peak-topeak noise trade-off," *EDN*, May 15, 2008, pg 26, www.edn.com/article/ CA6558465.

Baker, Bonnie, "What's in your SAR-ADC application?" EDN, Dec 15, 2008, pg 22, www.edn.com/ article/CA6622866.

Baker, Bonnie, "Analog filter eases delta-sigma-converter design," *EDN*, June 12, 2008, pg 24, www.edn. com/article/CA6566532.

Bonnie Baker is a senior applications engineer at Texas Instruments and author of A Baker's Dozen: Real Analog Solutions for Digital Designers. You can reach her at bonnie@ti.com.

# Why is Agilent the fastest growing oscilloscope manufacturer?

## Because we listen to you.

To build our scopes, Agilent carefully examines the challenges you face. Then we deliver products that solve your problems in imaginative ways. Like the multi-chip module that enables Infiniium's industry-leading signal integrity. And the ASIC that underlies InfiniiVision's patented Mega*Zoom* deep memory giving you the industry's best signal visibility. You'll find innovations like these in each of our scopes — that's why more and more engineers are choosing Agilent over other scope brands.\*

#### Agilent 20 MHz to >90 GHz real-time and sampling scopes

- · Handhelds, portables, rack-mounts and benchtops

- · 40+ application-specific software packages for exceptional insight

- · Innovations that satisfy your toughest demands

See why more and more engineers choose Agilent. Download our catalog www.agilent.com/find/scopecatalog

© Agilent Technologies, Inc. 2008 \*Prime Data August 2008 CAGR T&M Report

u.s. 1-800-829-4444 canada 1-877-894-4414

#### **PRY FURTHER AT EDN.COM**

+ Go to www.edn.com/090219pry for an expanded version of this article.

# A tale of two digital-video converters

SOFTWARE VERSUS HARDWARE COMPRESSION DEFINES THE DIFFERENCE.

hese digital-video converters offer similar functions; the less expensive unit even offers a TV tuner absent from its pricier peer. Plextor's ConvertX PX-TV100U cost \$8.99 after rebate, \$38.99 before rebate, and \$99 original MSRP (manufacturer's suggested retail price); the PX-M402U was \$29.99 after rebate, \$99.99 before rebate, and \$159 original MSRP. The big difference? A software- versus hardware-compression emphasis.

Plextor's PX-TV100U relies on the CPU horsepower of a USB2-tethered PC to handle the hefty audioplus-video lossy-compression duties. The PX-M402U harnesses its integrated WIS Technologies G07007SB streaming media encoder for these meaty tasks.

> Raw audio and video conveyance to a PC is the responsibility of the PV-TV100U's Empia Technology EM2860 USB2 media-capture processor. The USB2 transport of compressed multimedia data from the PX-M402U falls to Cypress Semiconductor's CY7C68013 embedded microcontroller.

PX-TV100U

The PX-M402U design offers flexibility in both primary PCB (printed-circuit-board) unpopulated sites and sufficient enclosure space for a supplemental PCB-based TV tuner that would transform the unit into a PX-TV402U. Similarly, although the PX-TV100U includes an LG Electronics "can" tuner, Plextor also sold the PX-AV100U, a tunerless variant of this design.

> Both devices need to translate analog multimedia information into digital equivalents. With the PX-TV100U, audio and video conversion are the domains of Micronas' MSP 3425G sound processor and Texas Instruments' 5150AM1 video decoder, respectively. The PX-M402U, conversely, relies on AKM Semiconductor's 5355 dualchannel, 16-bit audio ADC and NXP Semiconductor's SAA7115 video decoder. Whereas the SAA7115 comprehends NTSC (National Television System Committee), PAL (phase-alternating-line), and SECAM (Séquentiel Couleur Avec Mémoire) video standards, the video decoder in the PX-M401U (the PX-M402U's predecessor) supported only NTSC.

Both products include serial EEPROMs: a 1-Mbit Atmel 24C01A device in the PX-M402U and a 2-Mbit Catalyst Semiconductor 24WC02 memory for the PX-TV100U. The PX-M402U also embeds a 64-Mbit, PC100 SDRAM, Micron Technology's 48LC2M32B2 with a 32-bit interface.

PX-M402U

#### THAT'S MODEL-BASED DESIGN.

To create a two-mode hybrid powertrain, engineers at GM used models to continuously verify their design, test prototypes, and automatically generate the embedded code. The result: a breakthrough HEV, delivered on time. To learn more, visit mathworks.com/mbd

nce upon a time, you verified a logic design for an FPGA by compiling it, loading it, and pushing the reset button on your evaluation board. But, as FPGAs have become larger, this "blow-and-go" verification style, as Xilinx's director of software-product marketing, Hitesh Patel, terms it, has become counterproductive. The odds of creating a multimillion-gate design so close to perfection that

you could debug it from the pins on the package are vanishingly small. So, design teams have begun to employ software-based simulation of the design, much as ASIC teams have done for years.

# VERIFYING FPGA DESIGNS: SIMULATE, EMULATE, OR OPEFOR THE BEST?

SIMULATION IS A FACT OF LIFE FOR MANY FPGA USERS TODAY. BUT WHEN IS IT TIME TO STOP SIMULATING AND JUST DROP THE DESIGN INTO THE CHIP?

#### BY RON WILSON . EXECUTIVE EDITOR

But this approach raises a series of important questions: Should the role of simulation in an FPGA design be the same as it is in an ASIC design? Should the verification team still, at some point, just put the design in the target FPGA and start testing it at speed? If so, when is that point? To find out what design teams are doing today, we asked some of the people who work most closely with FPGA users. And, for reference, we asked a few ASIC design teams who use FPGA prototypes in their verification processes for their views, as well.

#### **PROS AND CONS**

Most people begin discussing the question of verification flow by assessing the relative strengths and weaknesses of simulation versus in-FPGA verification. At the risk of boring the experienced, this article will follow the same formula.

The huge advantage of simulation, of course, is access. You can observe any signal in an RTL (register-transfer-level) design down to clock-cycle resolution. You can control the state of the design to whatever degree you find worthwhile. Your knowledge of the RTL and your skill with the simulation environment are the only limits to observability and controllability. You can work interactively on limited areas of a design, or you can set up grand experiments that may run for days. And the relatively speedy setup of simulation runs makes it possible to quickly try lots of things.

Another advantage of simulation is that most simulation environments today are friendly to the use of OVL (Open Verification Library) or SystemVerilog assertions. Often, there is a straightforward way to transport these assertions into the simulation environment. As assertion-based verification becomes more common, this issue becomes important. In addition, the simulation environment allows you to keep your provisions for stimulating and observing the design separate from the design itself. This consideration might seem secondary, but it can become important in preserving the integrity of the design through intensive verification work.

But simulation is slow. "If you are doing 2 [million]- or 3 million-gate blocks, simulation is great," says Lauro Rizzatti, vice president of marketing at hardwareemulation vendor Eve. "But, at the multiple-block level, simulation can slow down until it is no longer useful."

The complexity of the design is not the only limitation. Phil Simpson, senior manager of technical marketing at Altera, points out that, if the design inherently requires huge amounts of data for validation, simulation may become impractical even at the block level. He offers the example of a video codec, which has so much internal state that a bug may appear only in the middle of a 15-minute video clip. But simulating the compression and decompression of 15 minutes of high-definition video could take most of a career.

#### **THE IN-CIRCUIT ARGUMENT**

The strengths and weaknesses of in-FPGA verification precisely complement those of simulation. To begin with the obvious, the FPGA is fast. Often, you can run the design at full speed, although, in some cases, this approach may mean more fussing with timing closure than you would want to do early in the design. And, unlike simulation, the FPGA doesn't necessarily slow down as you integrate more blocks into the design. So, it becomes possible to test the entire design rather than individual blocks and to run tests with large real-life data sets instead of surgically crafted test cases.

Because of the speed and the fact that the FPGA has the actual I/O cells that the design requires, you can also test the design in-system: either in an FPGA-development board that you have lashed into the target system or in the target PCB (printed-circuit board) if it is ready to go. Such testing eliminates the lingering uncertainty about whether the test cases really reflect the operating environment of AT A GLANCE Large-FPGA designs require an ASIC-like design flow.

Blending simulation and FPGAbased emulation in a verification flow is necessary.

There are no established guidelines for blending simulation.

A quick survey suggests a consensus on a verification flow for advanced-FPGA designs.

the design. Also, testing the design in its actual board can uncover I/O-related issues—electrical problems, signal-integrity issues, or incompatibilities in highspeed serial protocols, for example—that would be virtually undetectable in any other way. And in-system test creates a software-test platform as a side benefit.

These benefits all pertain to systemlevel verification. But Altera's Simpson points out that there are some interesting advantages for in-chip debugging of blocks, as well. "Once you get a block into the FPGA, you can use an embedded-processor core, such as Nios, to assist in the debug process," Simpson observes. "The core can move test data on and off the chip, for instance, and it can sequence the tests. In this way, you can test a block in isolation before the circuitry around it is ready.

"In our own IP [intellectual-property]-development group, we have written transactors to run on a Nios core to generate pseudorandom tests," Simpson continues. "I don't know that this practice is common among customers yet, but it can be quite valuable."

With all the advantages of FPGAs, you might wonder what's wrong with just dropping a newly coded core into the FPGA, coding up a test fixture around it, and starting to test. The answer to that question lies in the FPGA's disadvantages.

#### **FPGA WEAKNESSES**

The first and most obvious problem is visibility. In principle, every logic element in the FPGA is visible through the chips' debugging interface. But—rather surprisingly, given the power the internal debugging ports offer—vendors estimate that only about half of FPGA users actually synthesize the debugging interfaces into their designs and use them for verification. Xilinx's Patel thinks that num-

# Amped Up! Ready to Go!

ber may be growing as FPGAs get larger.

So, for the most part, if you want to observe a signal in your design, you have to route it out to a pin so that you can put a logic analyzer on it. Given the nature of logic analyzers, you may have to route out a number of other signals, such as internal clocks, as well. This approach means extra work, and it may mean having to reduce the clock frequency on the FPGA if you are trying to observe a fast signal that's nowhere near the I/O blocks. Hence, some managers say that it is vital to include your requirements for observability of FPGA signals in your original verification plan.

The added design work to get access to the signal is one disadvantage. But another problem with stimulating and observing internal nodes in the chip is that it requires you to change the design, rebuild, and resynthesize, risking a clean separation between the design and

the testbench. Without careful separation of debugging code from design code and fanatical version control, you can lose track of these changes, risking the equivalent of leaving surgical tools inside the patient. Then, there is the disadvantage of setup time. Synthesis times for large designs are not trivial, and the time to insert instrumentation, rebuild, resynthesize, and remap the design can become a factor in whether to perform a particular experiment. Incremental-synthesis tools can help here, but a 20 million-gate design can mean an overnight build-andsynthesis process.

Finally, there is the problem of transporting the testbench from the simulation environment to the FPGA environment. Stimulating a block now requires circuitry instead of a set of simulation commands. Observing a node requires circuitry and physical instruments, not just commands. And no one seems to have developed a way of systematically moving assertions from the simulation environment to the FPGA, despite the growing acceptance of assertion-based verification. "There is no solution today

#### SHINING SOME LIGHT ON THE COVERAGE GAPS

Everyone is in favor of the speed of in-FPGA emulation. But the difficulty of setting up, controlling, and observing experiments in an FPGA often forces laborious and time-consuming tests back into the simulation environment. In an ideal world, someone would put together a verification platform that combined the execution speed of FPGAs with the easy setup and excellent access of simulation. Not surprisingly, some vendors have targeted this ideal.

The first efforts, dating back to early in the ASIC era, were "big-iron" logicemulation systems. These systems are, in effect, specialized mainframe computers in which either custom microprocessors or custom programmablelogic devices simulate or emulate, respectively, the operation of the logic. A representative of such systems would be the **Cadence Palladium. The** systems offer many times the execution speed of simulation, with what the vendors would argue is at least equal access to the design under test. But they are limited in their capacity to not much more than the size block that you conveniently simulate-unless, that is, you have an impressive capital budget. These systems are major capital investments and therefore beyond the range of most design teams targeting FPGAs for the final design.

In recent years, a number of systems have entered the market-from companies such as Eve-that perform logic emulation in lean environments using commercial FPGAs. Such systems vary in personality from being mini-mainframe-emulation systems to being basically FPGA-evaluation boards with supporting debugging software. In all cases, the attempt is to provide an FPGA-execution environment with less logic overhead in the design than would be the case with a big-iron emulation system. **Because of their lower** overhead, the FPGA-based systems can often run one to a few orders of magnitude faster than the mainframe-emulation systems. In general, the faster they run, the less convenience of simulation they can preserve. But they run into limitations when a design, including the debugging overhead, is too large for a single FPGA. Partitioning the design is complex and often involves multiplexing signals between FPGAs. which slows everything down.

These systems do offer the software support necessary to move testbenches and data back and forth between the FPGA system and the simulation environment. Eve, for one, reports being at work on a way to import assertions into its environment, as well.

An interesting variation on this theme is the GateRocket system, which the company positions as either a simulation accelerator or an in-circuit emulator. As a simulator accelerator, the system attempts to just slip into the user's simulation environment, accelerating simulation of time-consuming pieces of the RTL (register-transferlevel) logic without disturbing the features of the environment. Assuming the 90/10 rule-that 90% of the simulation time goes into 10% of the code-this ability allows verification engineers to continue using the simulation environment further into the verification flow than would be practical without acceleration. GateRocket claims to support what it calls a synthesizable subset of assertions.

for automatically moving assertions to the FPGA, but we are getting more requests for this capability," Simpson says.

Another weakness here is coverage metrics. Although simulation environments are developing sophisticated tools to measure verification coverage and fuse measurements from different kinds of tools, the notion of coverage barely exists in the FPGA world, and there are no established tools for measuring test coverage of a design and reporting that data back to a central coverage-closure system.

#### WATCH THE ASIC TEAMS

So there, in a nutshell, are the advantages and disadvantages of each approach. Given that information, how do experienced ASIC design teams—who often employ FPGAs during their own verification flows—balance simulation and FPGA-based testing?

One answer comes from video-processor vendor Ambarella. Executive Vice President Didier LeGall says, "Mostly, we do not use FPGA emulation at all. Our experience has been that, for emulation to work, you need to have very mature RTL. But, by that stage in the flow, [the process of] getting the design into an FPGA and setting up a testbench is a lot of work with little return."

The application may condition Le-Gall's view. Ambarella SOCs (systems on chips) process high-definition video and 10M-pixel still images at high frame rates and require fast internal clocks and complex algorithms. But LeGall follows his comments on FPGA emulation with an interesting point about the objectives of the whole verification process. "The secret of first-time-working ICs is not perfect verification," LeGall says. "It is software": That is, know where the risk areas are in your design, and plan for software workarounds from the beginning, not as afterthoughts. This strategy does reduce the value of much of the information that verification engineers can glean from extensive FPGA-based testing.

Another view comes from LSI Corp's storage-components group. Bill Wuertz, vice president and general manager of the group, describes how that team does SCSI (small-computer-system-interface) and SAS (serial-attached-SCSI) controllers.

Wuertz says that LSI uses a nearly parallel process, with one verification team working in simulation with one set of objectives while another team works on FPGAs with a different set of objectives. "Early in the design, we create a step we call trial RTL," Wuertz says. "This is the first point where we feel the RTL is basically functionally correct and that the blocks are connected to each other. At this stage, the verification splits into two tracks. The simulation team compiles the design for their tools and goes to work on the individual blocks. A separate team, the systems-engineering group, synthesizes the RTL for an internally developed FPGA board—we are

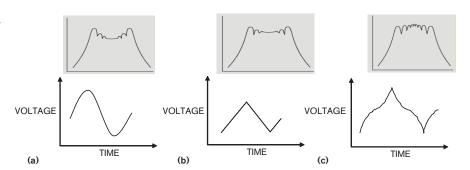

Figure 1 Three approaches to blending simulation with in-circuit debugging show the variety of verification flows teams are using today: traditional FPGA user (a), traditional ASIC designer (b), and the emerging blended approach (c).

on our fifth generation of the board design now—and begins exhaustive stress testing at the systems level."

As Wuertz describes it, the two groups have different purposes. The simulation team is trying to ensure that the circuitry is correct. The systems team is mostly unconcerned with the circuitry but is verifying that the chip works in the incredibly varied and complex environments of storage networks. Wuertz says that the FPGA prototype may run multiday tests connected to a room full of disk and tape drives. "These tests have evolved over 20 years," he says. "We've learned that it can take very long tests with a mix of different disk drives and tape units to generate just the odd timing alignment that will break the design."

LSI has worked out its own internal tools for linking the two environments. These tools allow the system team to

# Check real-time availability

Order with your credit card

(F) Ships within 2 business days

intersil.com/ibuy

# the EVOLUTION of ANALOG™

# Precisely What You Need!

### Micropower Precision Op Amps

- Main Instrumentation Amplifiers

- Current-Sensing Amplifiers

- Precision Voltage References

- Analog-to-Digital Converters

#### Digital Potentiometers (DCPs)

intersil.com/pinpoint

the EVOLUTION of ANALOG™

capture a trace leading up to a failure and convert that data to a stimulus file for the simulation team, for example. Conversely, the simulation team can alert the system team to any risk areas it sees in the design. Establishing communications between the two verification teams in their different environments has been crucial to LSI's two-track approach. The two exchange data throughout the process, and, in the end, the design manager requires closure from both teams.

#### **A CONSENSUS METHODOLOGY**

From discussions with FPGA vendors and users, we can see a consensus on a verification flow that blends simulation with emulation (**Figure 1**). Such a flow begins with block-level simulation of the design—not the exhaustive, strive-forperfection simulation of ASIC heritage, but more of a reality check. The objective is to verify that the block is functioning, that it is doing more or less the right thing at its pins, and that it can meet timing on an FPGA in a lab environment.

At this point, many teams move a version of the block to the FPGA and begin more exhaustive in-circuit testing. This case holds particularly true if the block, such as a video codec, requires long streams of high-speed data to verify correct functioning or if the block includes high-speed-I/O functions. In other cases, simulation work continues on the blocks until all are ready for integration.

Consensus suggests that, when the team begins to integrate blocks—the trial-system build—the FPGA really comes into its own. Here, the design may simply be too large for fast simulation. Or, with the known-working blocks, it may be more productive to troubleshoot integration issues on the FPGA than on the simulator.

But the consensus also suggests that the move from simulation to emulation is not a single irreversible step. Simulation work continues during system emulation, just as it runs in parallel with software development. And most teams use the FPGA emulation to capture and iso-

+ Go to www.edn.com/090219df and click on Feedback Loop to post a comment on this article.

+ For more technical articles, go to www.edn.com/features.

#### FOR MORE INFORMATION

Altera www.altera.com Ambarella www.ambarella.com Cadence www.cadence.com Eve www.eve-team.com GateRocket www.gaterocket.com LSI www.lsi.com Xilinx www.xilinx.com

late bugs and then pass them back to the simulation team for diagnosis. It is just too painful to do detailed diagnosis on the FPGA.

That summary describes what appears to be happening today, and it points out several serious weak spots in the method. First, it is difficult to move testbench data back and forth between environments. There seems to be no automatic mapping from simulation directives that create a test to FPGA structures that implement the same test. Second, embedded-RISC cores, available from all major FPGA vendors, appear to be a vastly underused resource-able to manage data and control tests but isolated from the simulation testbench. In principle, the simulation team could move its testbench into C code for the embedded core, rather than into RTL for the FPGA. Third, there is no simple path from the data a team collects in an FPGA experiment back to the simulation bench. And, finally, as the use of assertion-based verification grows in the simulation world, the situation cries out for a similar assertionbased tool on the FPGA side.

One indication that these issues are valid is that vendors selling FPGAbased emulation systems address each of them (see **sidebar** "Shining same light on the coverage gaps"). Examples include systems from Eve; simulation accelerators, such as GateRocket; and "big-iron" emulation boxes, such as Cadence's Palladium. Whether this infrastructure will evolve for the ad hoc board-level emulations typical of the FPGA-verification world or whether it will remain the differentiation of bigticket simulation accelerators and emulation systems remains to be seen.**EDN**

You can reach Executive Editor Ron Winor at 1-408-345-4427 and ronald.wilson@ reedbusiness.com. Intersil Micropower Op Amps

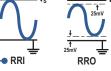

#### Intersil's pinPOINT<sup>™</sup> Precision Analog Product Line now has two single-supply op amps that consume less than 1µA.

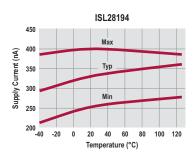

Intersil's ISL28194, with a typical supply current of just 330nA, consumes less than half the power of the closest competitor. The ISL28195 boasts a gain bandwidth of 10kHz on just 1µA.

to 5.5V and ideal for low-power precision applications that run on 1.5V alkaline batteries.

Ultra-Small Packages 6 Ld SOT-23 6 Ld µTDFN

Rail-to-Rail Input/Output Allows full dynamic range and maximum battery usage.

True rail-to-rail input simplifes system design and supports maximum signal levels.

#### Other Members of Intersil's Nanopower Family

| intersit's Natiopower Failing |                                                          |  |  |

|-------------------------------|----------------------------------------------------------|--|--|

| I <sub>SS</sub> /Amp (typ)    | Function                                                 |  |  |

| 330nA                         | Op Amp                                                   |  |  |

| 1µA                           | Op Amp                                                   |  |  |

| 2.5µA                         | Comparator                                               |  |  |

| 800nA                         | Comparator                                               |  |  |

| 400nA                         | Voltage Reference                                        |  |  |

| 500nA                         | Voltage Reference                                        |  |  |

|                               | Iss/Amp (typ)<br>330nA<br>1μA<br>2.5μA<br>800nA<br>400nA |  |  |

📍 intersil.com/pinpoint © 2008 Intersil Americas Inc. All rights reserved. the EVOLUTION of ANALOG"

# MAKING OSCILLATOR SELECTION CRYSTAL CLEAR

#### **BY PAUL RAKO • TECHNICAL EDITOR**

SILICON AND MEMS OSCILLATORS ARE JOINING VENERABLE QUARTZ CRYSTALS AND CERAMIC RESO-NATORS IN THE HIGHLY DIVERSE OSCILLATOR MARKET. YOU DON'T NEED A CRYSTAL BALL TO SELECT THE RIGHT DEVICE FOR YOUR APPLICATION, BUT SOME PERTINENT FACTS WILL HELP.

Oscillators are as ubiquitous—and, some might argue, as important—as power supplies in electronics systems, finding use in anything that needs a timing signal, from digital watches to TVs and PCs. Because of their important role in timing for electronics, their failure can bring down an entire system. For example, investigators in

1972 traced the cause of a train crash in Fremont, CA, to a faulty crystal oscillator on a control board. An inappropriate value for the oscillator's tank capacitor overdrove the crystal, causing the part to jump into an overtone frequency. As a result, the train

sped up rather than slowed down as it approached a station, and the resultant crash caused many injuries. Because of problems such as this one, many engineers have stopped using raw crystals to make their own oscillators. Instead, they buy off-the-shelf components whose packages contain the amplifiers, tank capacitors, and other parts.

All digital devices require clock

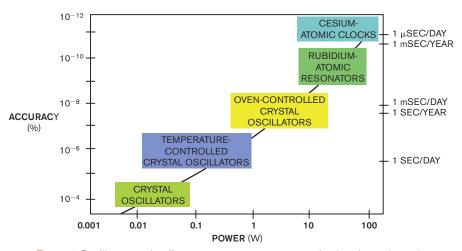

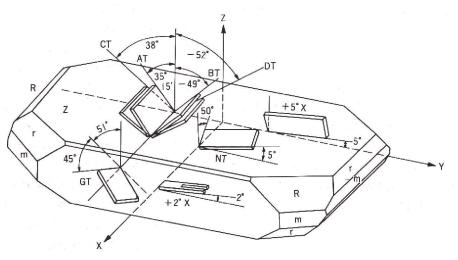

sources, such as silicon and MEMS (microelectromechanical-system) oscillators, quartz crystals, or ceramic resonators. Telecommunications and servers, for example, might need a dozen clocks on a single PCB (printedcircuit board). Designers have implemented traditional clock sources with quartz-crystal resonators, but MEMS and pure-silicon resonators are gaining a foothold in this highly diverse market. In addition, less accurate resonators employ ceramic materials, such as lead-zirconium titanate. The application drives the suitability of a technology. For example, if you need a clock source with better than 1-ppb (part-per-billion) accuracy, you must abandon MEMS devices and instead use atomic-resonance devices, such as rubidium- or cesium-clock sources. These devices have 1-ppt (part-pertrillion) accuracy. A GPS (global-positioning-system) satellite, for example, needs this accuracy to maintain synchronicity with the rest of the system (Figure 1).

The humble ceramic resonator lies at the opposite end of the accuracy spectrum. You measure the accuracy of these devices as percentages because the parts-per-million measurement yields an unwieldy, large number. The typical initial accuracy of a ceramic resonator ranges from 0.5 to 0.1%, and drift due to aging or temperature

changes can alter this range. As a result, an inexpensive ceramic oscillator can have a tolerance of only  $\pm 1.1\%$ , whereas higher-end automotive and commercial products can have accuracies of  $\pm 0.25$  and  $\pm 0.3\%$ , respectively. These tighter-tolerance ceramic resonators target use in USB (universal-serial-bus) 2.0 circuits in commercial and automotive CAN (controller-area-network)bus applications that operate at -40 to +125°C. Low-cost ceramic resonators, at frequencies of 200 kHz to almost 1 GHz, work well in embedded systems in which timing is not critical. Ceramic devices offer faster start-up and are often smaller than their quartz counterparts. They are also more tolerant of shock and vibration. Ceramic resonators are available from such manufacturers as Murata, Oscilent, AVX, TDK, and Panasonic.

For digital systems using UARTs (universal synchronous/asynchronous transceivers), you should do an error-budget analysis to ensure that the baud rate you derive from the resonator frequency stays in spec. If you use the UART only during code development, you might be able to switch in a ceramic resonator in production and save money.

Note that some silicon oscillators use RC (resistance/capacitance) or LC (inductance/capacitance) tanks and no ceramic or quartz. These oscillators also have a broad range of accuracy commensurate with their price. Companies

#### AT A GLANCE

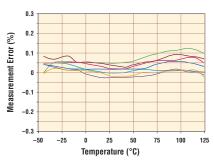

Ceramic resonators have accuracy of 1 to 0.1%, compared with 1 to 100 ppm (parts per million) for quartz oscillators and 1.5 to 100 ppm for silicon devices.

Silicon and MEMS (microelectromechanical-system) oscillators are more resistant to shock and fit into smaller packages than can ceramic devices.

Quartz oscillators take longer to start but typically use less power than other types.

Power consumption of any oscillator type depends on output loading.